# MULTI-RESOLUTION ANALYSIS BASED ANN ARCHITECTURE FOR FAULT DETECTION IN DC MICROGRIDS

Don Kasun Joseph Shan Jayamaha

178058L

Degree of Master of Philosophy by Research

Department of Electrical Engineering

University of Moratuwa

Sri Lanka

February 2020

# MULTI-RESOLUTION ANALYSIS BASED ANN ARCHITECTURE FOR FAULT DETECTION IN DC MICROGRIDS

Don Kasun Joseph Shan Jayamaha

178058L

Thesis submitted in fulfillment of the requirements for the degree of Master of Philosophy by Research

Department of Electrical Engineering

University of Moratuwa

Sri Lanka

February 2020

## DECLARATION

I declare that this is my own work and this thesis does not incorporate without acknowledgement any material previously submitted for a Degree or Diploma in any other University or institute of higher learning and to the best of my knowledge and belief it does not contain any material previously published or written by another person except where the acknowledgement is made in the text.

Also, I hereby grant to University of Moratuwa the non-exclusive right to reproduce and distribute my thesis, in whole or in part in print, electronic or other medium. I retain the right to use this content in whole or part in future works (such as articles or books).

Signature:

Date:

The above candidate has carried out research for the Masters/MPhil/PhD thesis / Dissertation under my supervision.

Signature of the supervisor:

Date

Signature of the supervisor:

Date

## ABSTRACT

DC microgrids present an effective means for integration of renewable energy sources to the utility network while offering clear benefits such as higher efficiency, better compatibility with DC sources and loads and simpler control, compared to its AC counterpart. However, protection challenges associated with DC networks, such as lack of frequency and phasor information, lack of standards, guidelines and practical experience are of particular concern.

Lack of effective solutions for protection of DC networks presents a major barrier for the widespread integration of DC microgrids to the utility network. There are several conventional DC network protection techniques employed in wide range of DC network applications in the fields of telecommunication, data centers and shipboard networks. However, straightforward application of these conventional techniques for protection of DC microgrids is impracticable due to intermittent nature of DGs connected to the network, operation in both grid-connected and islanding mode and high sensitivity to fault impedance.

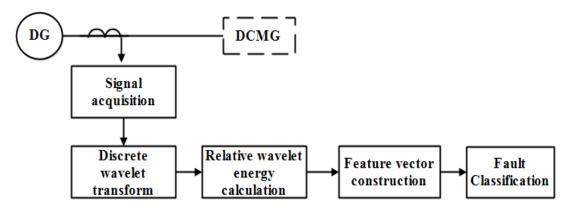

Hence, for the safe operation of DC microgrids, it is imperative to have reliable fault detection and relay coordination scheme. This thesis presents novel fault detection and grounding scheme for DC microgrids. In the proposed fault detection scheme, fault features contained within fault transients are extracted using a multiresolution analysis technique and are used alongside an ANN classifier scheme for fault classification.

To evaluate the performance, a comprehensive study on the proposed scheme is presented. Simulation based test results asserted that the proposed technique has accurate, fast and intelligent fault detection capability compared to existing DC protection schemes.

Possible improvements to the current technologies and future directions for research, which could enhance the protection of DC microgrids, are also outlined in this thesis.

Keywords— Artificial Neural Networks, DC microgrid protection, Fault detection, Fault localization, Wavelet transform

#### ACKNOWLEDGEMENT

I would like to thank my supervisor Dr L.N.W Arachchige of Department of Electrical Engineering at University of Moratuwa, and Prof A.D Rajapakse of Department of Electrical and Computer engineering, University of Manitoba, Canada for accepting my proposal for the research. Under their direction, I was awarded full freedom to steer the research, but guide me in the right direction whenever they thought I needed it.

I like to specially thank to University of Moratuwa for the financial support under Senate Research Committee (SRC) Grant scheme (SRC/CAP/2018/01). Moreover, a special word of thanks is meant for my family for supporting me and encouraging me through the period. I would like to extend my gratitude for all research colleagues in Department of Electrical Engineering who helped me and motivated me during the research.

# CONTENTS

| DECLARATI    | ONi                                                  |

|--------------|------------------------------------------------------|

| ABSTRACT     | ii                                                   |

| ACKNOWLE     | DGEMENTiii                                           |

| LIST OF FIGU | JRESviii                                             |

| LIST OF TAB  | LESxii                                               |

| LIST OF APP  | ENDICESxiii                                          |

| LIST OF ABB  | REVIATIONS xiv                                       |

| 1. INTRODU   | CTION 1                                              |

| 1.1. B       | ackground1                                           |

| 1.1.1.       | DC Microgrids: a Future Power System1                |

| 1.2. P       | roblem Statement                                     |

| 1.2.1.       | Research Gap                                         |

| 1.2.2.       | Main Objectives                                      |

| 1.3. T       | hesis Overview                                       |

| 2. LITERATU  | URE REVIEW                                           |

| 2.1. D       | C microgrid protection challenges                    |

| 2.1.1.       | DC microgrids faults                                 |

| 2.1.2.       | Challenges: Fault detection and localization7        |

| 2.1.3.       | Challenges: fault current interruption               |

| 2.2. D       | C microgrid fault detection and localization schemes |

| 2.2.1.       | Overcurrent detection                                |

| 2.2.2.       | Derivatives of current                               |

| 2.2.3.       | Differential protection                              |

| 2.2.4.       | Distance protection                                  |

| 2.2.5.       | Signal processing based detection schemes11          |

| 2.2.6. Pattern recognition schemes                                                     |

|----------------------------------------------------------------------------------------|

| 2.3. DC microgrid protection coordination schemes                                      |

| 2.3.1. Protection coordination: time grading of relays                                 |

| 2.3.2. Protection coordination: communication based                                    |

| 2.4. DC microgrid fault interruption14                                                 |

| 2.4.1. Converter fault current blocking and current limiting techniques.15             |

| 2.4.2. Fault current limiters (FCLs)                                                   |

| 2.4.3. Fault current interruption with DC side circuit breakers                        |

| 2.5. DC microgrid modelling, control, experimental setups and standardizations aspects |

| 2.5.1. Overview on DC microgrid architectures                                          |

| 2.5.2. DC microgrid Control requirements                                               |

| 2.5.3. DC microgrid control hierarchy                                                  |

| 2.5.4. Load power sharing methods/ Primary control methods                             |

| 2.5.5. DC microgrid experimental setups worldwide                                      |

| 2.5.6 Standardization aspects of DC microgrids                                         |

| 2.6. Concluding remarks                                                                |

| DC MICROGRID MODELLING AND CONTROL                                                     |

| 3.1. DC Microgrid control strategy                                                     |

| 3.1.1. G-VSC control                                                                   |

| 3.1.2. Solar PV plant control                                                          |

| 3.1.3. ESS control                                                                     |

| 3.2. Battery Energy management system                                                  |

| 3.6.1. Operating mode 1                                                                |

| 3.6.2. Operating mode 2                                                                |

| 3.6.3. Operating mode 3                                                                |

3.

| 3.2.4. Operating mode 4                                         | 8 |

|-----------------------------------------------------------------|---|

| 3.3. Load shedding and generation curtailment                   | 9 |

| 3.4. DC microgrid model validation                              | 0 |

| 4. DC MICROGRID FAULT RESPONSE ANALYSIS                         | 5 |

| 4.1. DC mirogrid Transient behavior                             | 5 |

| 4.2. Power electronic converter behavior                        | 5 |

| 4.2.1. G-VSC post Fault behavior                                | 6 |

| 4.2.2. DC-DC converter post fault behavior                      | 7 |

| 4.3.Pole –pole fault: overall system response                   | 0 |

| 5. DC MICROGRID GROUNDING                                       | 3 |

| 5.1.Grounding design considerations in DC networks              | 3 |

| 5.2.DC microgrid grounding methods                              | 4 |

| 5.3.1. Solidly grounded AC utility network                      | 4 |

| 5.2.1. Ungrounded AC utility network                            | 9 |

| 5.3. Grounding system design : discussion                       | 1 |

| 6. DC MICROGRID FAULT DETECTION AND CLASSIFICATION SCHEME       | E |

|                                                                 | 2 |

| 6.1. Background                                                 | 2 |

| 6.2. Proposed algorithm for fault detection and localization    | 2 |

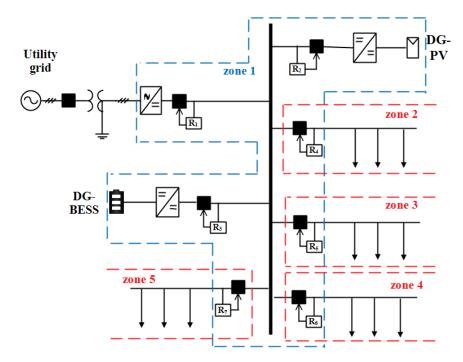

| 6.3. Proposed protection coordination strategy                  | 3 |

| 6.4. Signal processing and fault feature extraction             | 6 |

| 6.4.1. Wavelet theory and multi-resolution analysis             | 6 |

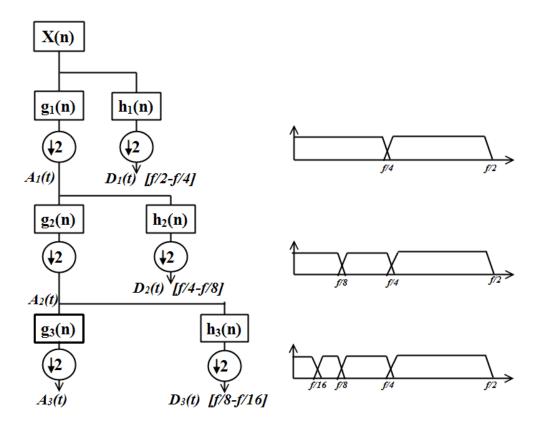

| 6.4.2. Multi-resolution analysis                                | 7 |

| 6.4.3. Signal pre-processing                                    | 8 |

| 6.4.4. Relative wavelet energy as an information tool           | 9 |

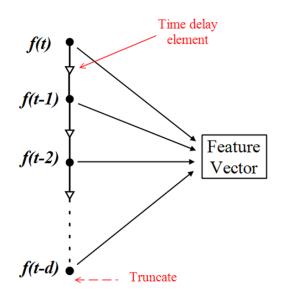

| 6.4.5. Sliding window technique for feature vector construction | 1 |

| 6.4.6. Feature vector construction                  |

|-----------------------------------------------------|

| 6.4.7. Feature vector comparison                    |

| 6.5 Fault classification96                          |

| 6.5.1. Classification methods97                     |

| 6.5.2. Classifier selection                         |

| 6.5.3. Structure of the ANNS                        |

| 6.5.4. ANN training100                              |

| 7. FAULT DETECTION AND LOCALIZATION PERFORMANCE 103 |

| 7.1.Classification accuracy                         |

| 7.2. Response time of the proposed schem 106        |

| 7.3. Robustness of the proposed scheme 106          |

| 7.4. Comparison with existing schemes107            |

| 7.5. Concluding remarks 109                         |

| 8. CONCLUSIONS AND CONTRIBUTIONS 110                |

| 8.1. Conclusions110                                 |

| 8.2. Contributions                                  |

| 8.3. Suggestions for future research114             |

# LIST OF FIGURES

| Figure 1. 1 Illustration of a DC microgrid                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2. 1 Classification of DC microgrid Faults7                                                                                          |

| Figure 2. 2. ETO thyristor based VSC architecture                                                                                           |

| Figure 2. 3 Back to back VSC architecture                                                                                                   |

| Figure 2. 4 DAB architecture with DC fault current limiting capability                                                                      |

| Figure 2. 5 Mechanical DC breakers with (a) passive commutation, (b) active commutation circuit                                             |

| Figure 2. 6 Solid-state circuit breaker assembly                                                                                            |

| Figure 2. 7 Z source circuit breaker circuitry                                                                                              |

| Figure 2. 8 Hybrid circuit breaker circuitry                                                                                                |

| Figure 2. 9 DC microgrid with (i) Radial configuration, (ii) Ring configuration, (iii) Mesh configuration and (iv) Zonal type configuration |

| Figure 2. 10 DC microgrid with (a) unipolar DC bus, (b) bipolar DC bus25                                                                    |

| Figure 2. 11 Hierarchical Control levels for DC microgrid system                                                                            |

| Figure 2. 12 Three level hierarchical control structure for DC microgrid                                                                    |

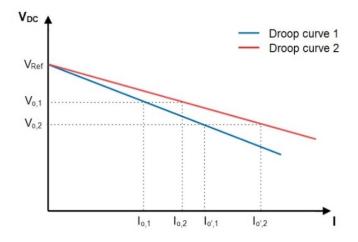

| Figure 2. 13 Conventional droop control characteristic curve                                                                                |

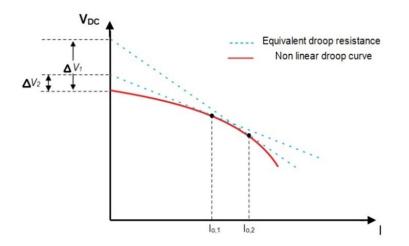

| Figure 2. 14 Non-linear droop control characteristic curve                                                                                  |

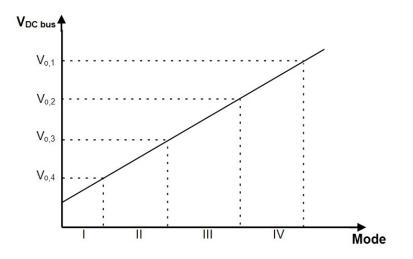

| Figure 2. 15 DBS control with four operating modes for a DCMG system                                                                        |

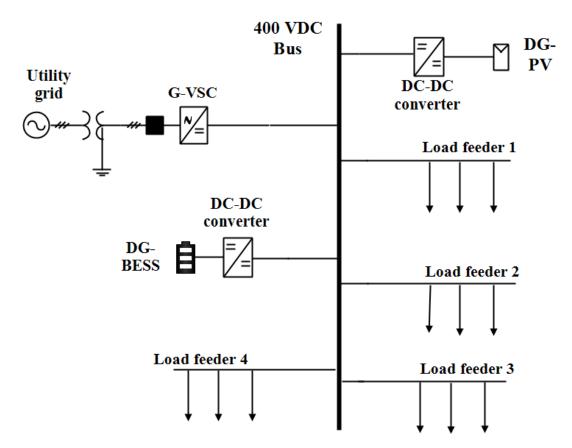

| Figure 3. 1 Notional DC microgrid model developed in PSCAD/EMTDC 42                                                                         |

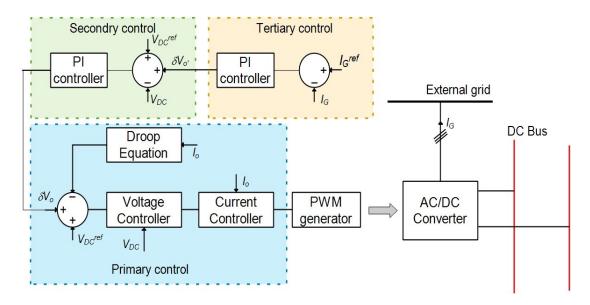

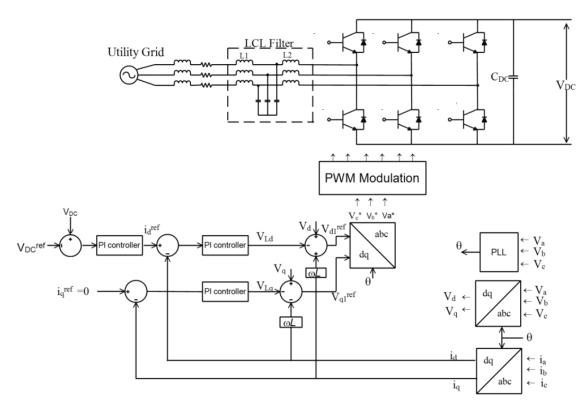

| Figure 3. 2 Schematic of the G-VSC control                                                                                                  |

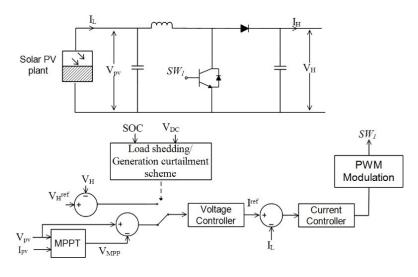

| Figure 3. 3 Solar PV plant control scheme                                                                                                   |

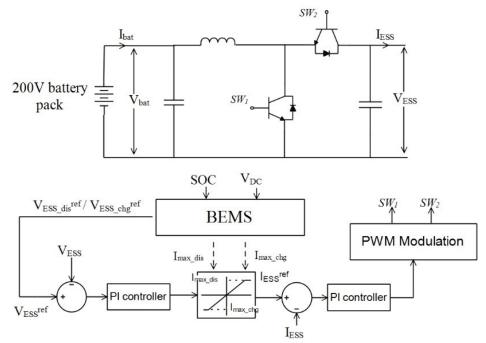

| Figure 3. 4 ESS control block diagram                                                                                                       |

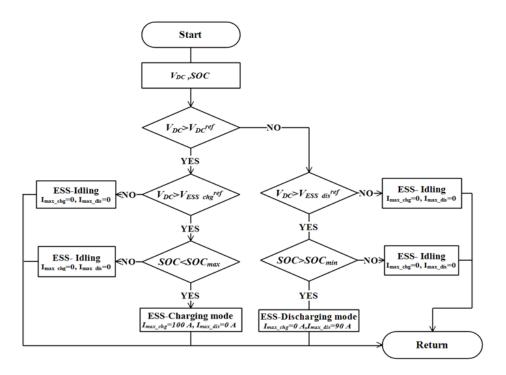

| Figure 3. 5 Proposed BEMS control algorithm for the DCMG model                                                                              |

| Figure 3. 6 Five-level voltage control hierarchy                                                                                            |

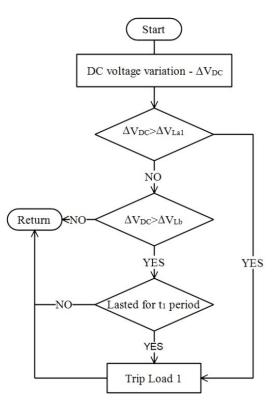

| Figure 3. 7 Proposed load shedding scheme for DCMG load feeders                                                                             |

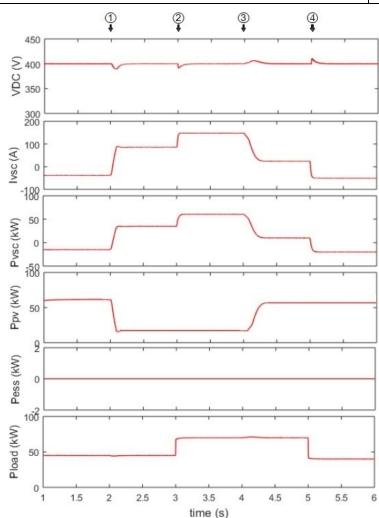

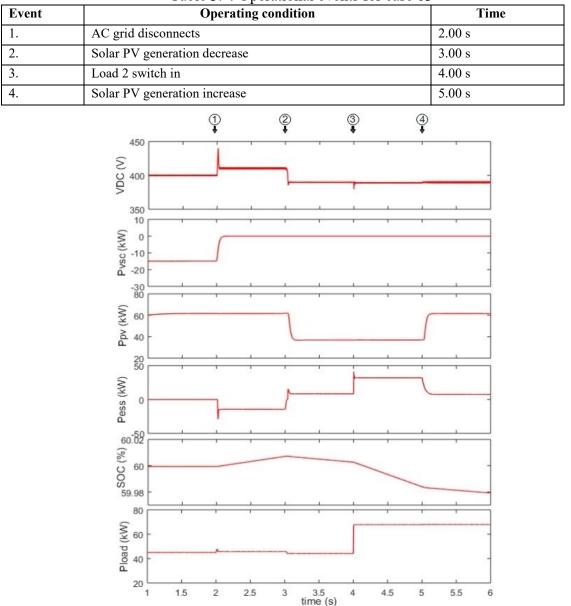

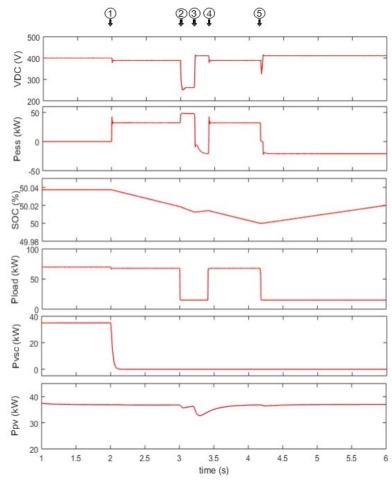

Figure 3. 8 Operation during grid-connected mode, (a) DC bus voltage, (b) G-VSC DC current, (c) G-VSC power, (d) solar PV power, (e) ESS power, (f) Load power 51

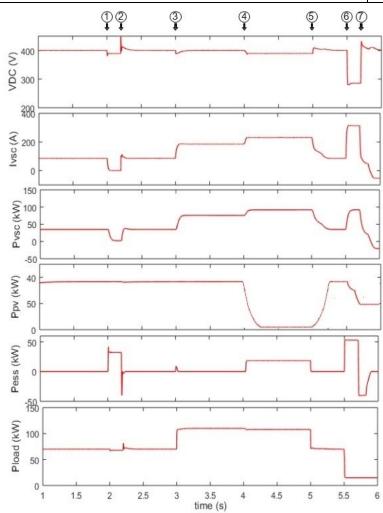

Figure 3. 10 Operation during islanded mode (case 3), (a) DC bus voltage, (b) G-VSC power, (c) solar PV power, (d) ESS power, (e) SOC level (f) load power...... 53

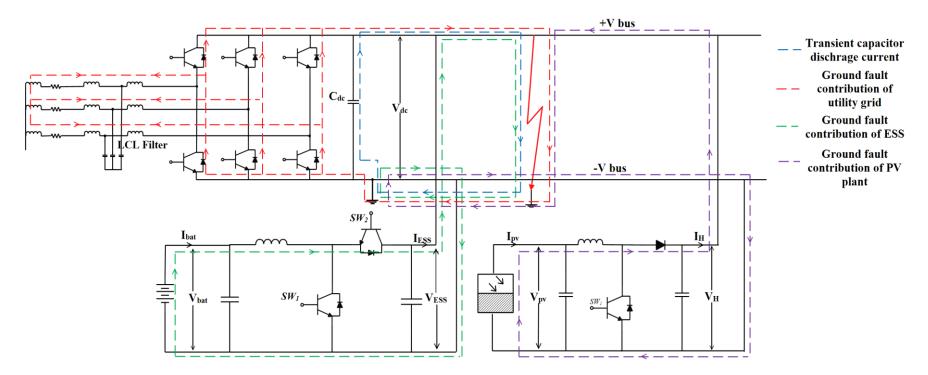

| Figure 5. 4 Ground fault current flow paths in a AC grid transformer neutral isolated,                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC negative bus solidly grounded DCMG70                                                                                                                                                                                                                                                                                 |

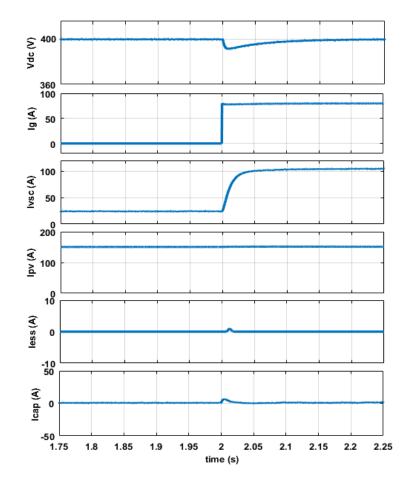

| Figure 5. 5 Trend of variation of (a) DC bus voltage, (b)ground fault current, (c) VSC current, (d) PV current, (e) ESS current, (f) capacitor discharge current, with a high $R_g$ ground fault in a DC negative bus grounded DCMG                                                                                     |

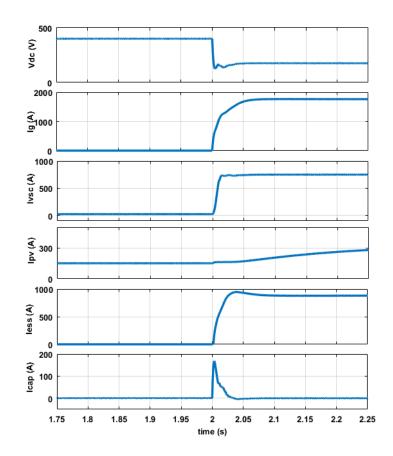

| Figure 5. 6 Variation of (a) DC bus voltage, (b) ground fault current, (c) VSC current (d) PV plant current, (e) ESS current, (f) capacitor discharge current, at a low $R_g$ ground fault, in a DC negative bus grounded DCMG                                                                                          |

| Figure 5. 7 Variation of (a) DC bus voltage, (b) ground fault current, (c) voltage between DC positive pole and ground, (d) voltage between DC negative pole and ground, at a low $R_g$ ground fault in a DC bus high resistance grounded DCMG 74                                                                       |

| Figure 5. 8 Ground fault current flow paths in a AC grid transformer neutral isolated, DC bus midpoint grounded DCMG                                                                                                                                                                                                    |

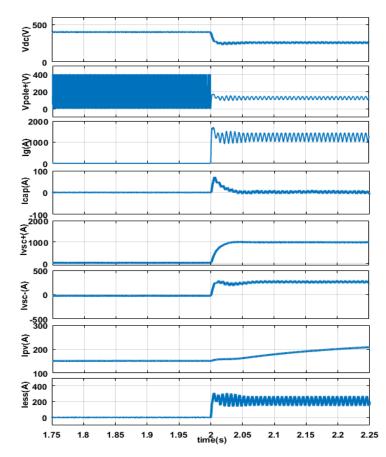

| Figure 5. 9 Variation of (a) DC bus voltage, (b) ground fault current,(c) voltage between DC positive pole and ground, (d) capacitor discharge current (e) VSC current, (f) ESS current, (g) PV plant current, (h) voltage between DC negative pole and ground, at a low $R_g$ fault in a DC bus midpoint grounded DCMG |

| Figure 5. 10 (a) Diode grounding configuration; (b) Thyristor grounding configuration                                                                                                                                                                                                                                   |

| Figure 6. 1 Basic structure of the proposed DCMG fault detection algorithm                                                                                                                                                                                                                                              |

| Figure 6. 2 Schematic of the notional DC microgrid model and the protection zones                                                                                                                                                                                                                                       |

| Figure 6. 3 DWT decomposition of signal with iterated filter banks, and frequency bands of different decomposition levels                                                                                                                                                                                               |

| Figure 6. 4 Sliding window technique to construct a spatial vector using temporal data                                                                                                                                                                                                                                  |

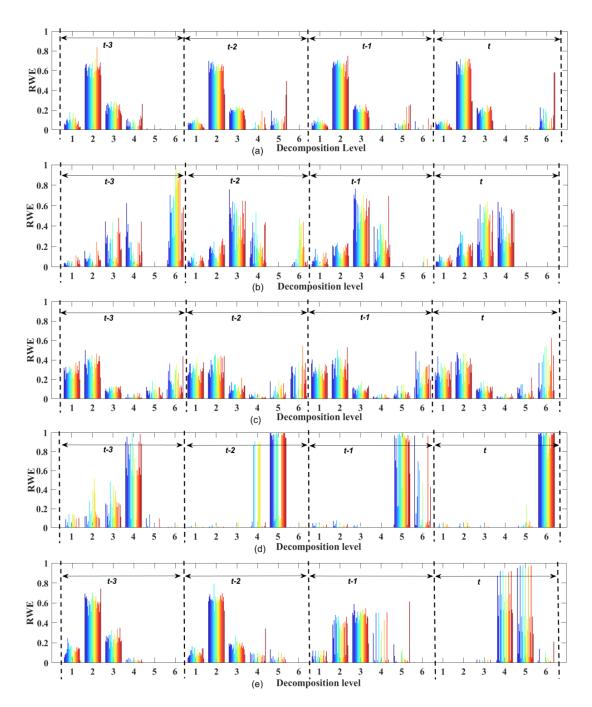

| Figure 6. 5 RWE distribution diagram of the feature vector extracted from a) current signals during 25 pole- ground faults b) current signals during 25 pole-pole faults c)                                                                                                                                             |

current signals during 25 normal operation conditions d) current signals during 25

| load switch in-out operations e) current signals during 25 fault interruption          |

|----------------------------------------------------------------------------------------|

| operations by the primary protection relay of a lateral feeder                         |

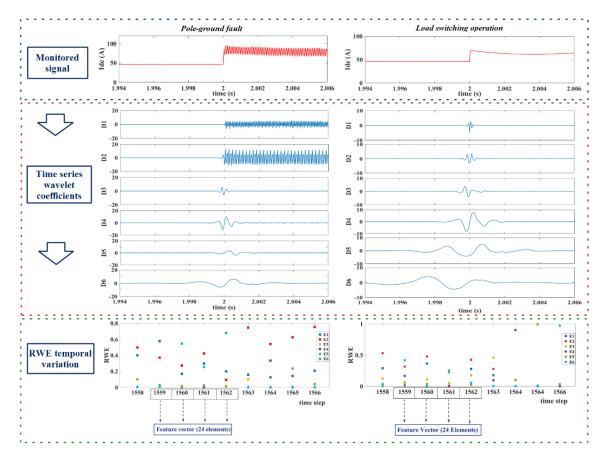

| Figure 6. 6 Intermediary stages of signal processing of current with pole-ground fault |

| (at t=2s), and load switching operation (at t=2s)                                      |

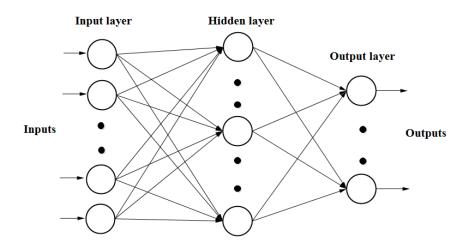

| Figure 6. 7 Basic structure of ANN for classification                                  |

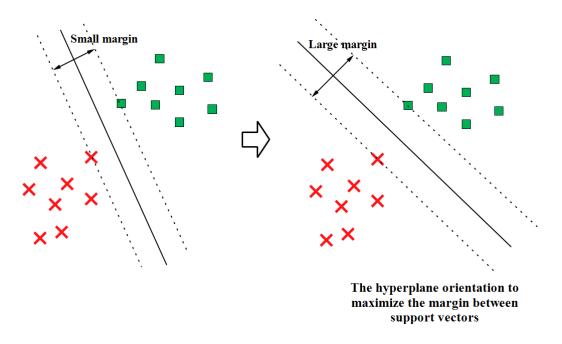

| Figure 6. 8 Illustration of the concept of support vector machines                     |

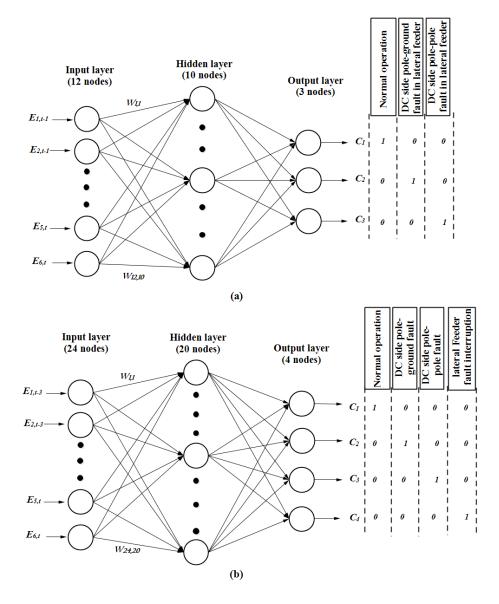

| Figure 6. 9 structure of the employed ANNs for fault classification in a (a) type I    |

| relay, (b) <i>type II</i> relay101                                                     |

| Figure 7. 1 Confusion matrix for test results obtained using test cases for relays (a) |

| R1, (b) R2, (c) R3, (d) R4, (e) R5, (f) R6, (g) R7104                                  |

# LIST OF TABLES

| Table 2. 1 DC microgrid experimental setups worldwide and their characteristic      features      36                           |

|--------------------------------------------------------------------------------------------------------------------------------|

| Table 2. 2 General description and scope/ primary goals of standards/standardization      efforts for DCMGs    39              |

| Table 3. 1 Characteristic data for the developed DCMG model in PSCAD/EMTDC                                                     |

| Table 3. 2 Operational events for case 01    51                                                                                |

| Table 3. 3 Operational events for case 02    52                                                                                |

| Table 3. 4 Operational events for case 03    53                                                                                |

| Table 3. 5 Operating events for case 04                                                                                        |

| Table 5. 1 DC microgrid grounding configurations, and their characteristic features.                                           |

| Table 6. 1 DCMG fault locations and corresponding protection devices selected forthe protection of DCMG network components     |

| Table 6. 2 Frequency bands of DWT decomposition levels, and minimum windowsize for RWE calculation in each decomposition level |

| Table 6. 3 Relay type selection and protected zones of the DCMG network       92                                               |

| Table 6. 4 Comparison between classifier models                                                                                |

| Table 6. 5 Architecture and learning parameters of ANNs employed for relay type I         and type II       100                |

| Table 6. 6 Different configurations for fault and non-fault simulation inPSCAD/EMTDC                                           |

| Table 7. 1 Fault detection accuracies of the proposed scheme for the test data      considered    105                          |

| Table 7. 2 Classification accuracy of relay $R_1$ with noisy current measurements 107                                          |

| Table 7. 3 Fault detection schemes for dc microgrids: comparison                                                               |

# LIST OF APPENDICES

| Appendix      | A: | MATLAB | code | for | DWT | decom   | position | and | RWE   | calcu | lation |

|---------------|----|--------|------|-----|-----|---------|----------|-----|-------|-------|--------|

|               |    |        |      |     |     |         |          |     |       |       | 131    |

|               |    |        |      |     |     |         |          |     |       |       |        |

| Appendix      | B: | MATLA  | B co | de  | for | trained | neural   | net | works | for   | fault  |

| classificatio | on |        |      |     |     |         |          |     |       |       | 133    |

# LIST OF ABBREVIATIONS

| DCMG  | DC microgrid                  |

|-------|-------------------------------|

| RE    | Renewable energy              |

| DG    | Distributed generator         |

| RES   | Renewable energy source       |

| ACMG  | AC microgrid                  |

| PV    | Photovoltaic                  |

| EV    | Electric vehicle              |

| ESS   | Energy storage system         |

| V2G   | Vehicle to grid               |

| DWT   | Discrete wavelet transform    |

| ANN   | Artificial neural network     |

| CB    | Circuit breaker               |

| ACCB  | AC circuit breaker            |

| HVDC  | High voltage DC               |

| MVDC  | Medium voltage DC             |

| IED   | Intelligent electronic device |

| di/dt | Derivative of current         |

| FTT   | Fast Fourier transform        |

| STFT  | Short-time Fourier transform  |

| WT    | Wavelet transform             |

| SVM   | Support vector machines       |

| ETO   | Emitter turn off              |

| MMC   | Modular multi-level converter |

| FCL   | Fault current limiter         |

| DCCB  | DC circuit breaker            |

|       |                               |

| SSCB  | Solid-state circuit breaker             |

|-------|-----------------------------------------|

| IGBT  | Insulated gate bipolar transistor       |

| IGCT  | Insulated gate commutated transistor    |

| ZSCB  | Z source circuit breaker                |

| SCR   | Silicon controlled rectifier            |

| SiC   | Silicon Carbide                         |

| GaN   | Gallium Nitride                         |

| HCB   | Hybrid circuit breaker                  |

| FMS   | Fast mechanical switch                  |

| G-VSC | Grid-connected voltage source converter |

| MPPT  | Maximum power point tracking            |

| SOC   | State of charge                         |

| BEMS  | Battery energy management system        |

| DESAT | Desaturation                            |

# 1. INTRODUCTION

This thesis presents an effective solution for protection of DC microgrid (DCMG) networks. This chapter covers the background to the research, motivation behind this research, main objectives and thesis overview.

#### 1.1. Background

In recent years, considerable research attention has been given towards renewable energy (RE) supply, to address the environmental issues due to conventional energy sources. Efforts to adopt clean energy sources have resulted in increased integration of distributed generators (DGs) such as solar PVs, micro wind turbines, and fuel cells. However, the increased penetration of DGs to the utility network has resulted in undesirable impacts such as; voltage rise, reduced power quality, protection coordination issues and system stability issues. Therefore, in order to accommodate higher penetration of renewable energy sources (RES), microgrids have become an attractive arrangement due to its controllable, reliable and intelligent energy routing capabilities [1-4].

Microgrid is an active distribution network consisting of DGs, energy storage elements and consumer loads, and is capable of operating either in synchronization with utility grid (grid-connected mode) or in islanded mode. The microgrid networks are capable of functioning autonomously whenever required, to adhere by the economic and operational demands. Microgrids are typically designed to achieve high reliability and uninterruptable power supply capability; hence is an effective solution to supply critical loads such as data center networks. Furthermore, microgrids reduce the energy burden to the conventional power generation and transmission infrastructure [1-5].

# 1.1.1. DC Microgrids: a Future Power System

DC microgrids are conceptual future power systems to meet the increasing energy demand and solve problems caused by conventional power sources, and are specially researched all around the world.

With the higher penetration of renewable based DG, such as solar PV arrays, together with the increasing use of electronic loads and Electric Vehicles (EVs), have

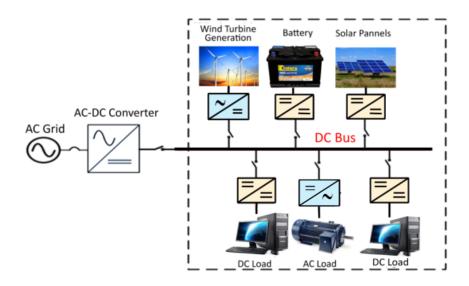

prompted the idea of using DC distribution systems. Also, with new innovations in the areas of smart homes/buildings, fast EV charging stations, V2G (Vehicle to Grid) technology, hybrid energy storage systems and renewable energy parks, DCMGs are becoming increasingly popular [6-10]. A wide range of traditional DC distribution applications in the fields of telecommunication, traction and vehicular systems can be classified under the DCMG framework and ongoing developments and trends in these fields are largely influential on the development and expansion of DCMGs [10-12]. Figure 1.1 is a representation of a DCMG system with RESs, which can operate in both islanded and grid-connected modes.

Figure 1. 1 Illustration of a DC microgrid

Advantages of DCMGs when compared to the AC microgrids are given below [7, 10]:

- i. DCMGs have the potential to provide more efficient solutions for integrating larger share of RES, improve the reliability, and efficiency of energy transfer.

- ii. Provide a natural interface with RESs, electronic loads and most energy storage systems (ESSs) reducing the cost and losses of conversion.

- iii. Eliminate the issues with harmonics, synchronizing, phase unbalances and voltage sags to a greater extent.

- iv. Requirement for control of reactive power flow is eliminated in DC microgrids.

- v. DGs in a DC microgrid do not easily trip against disturbances, meaning DC microgrids have a very good fault ride through capability.

# **1.2. Problem Statement**

The overall function of a DCMG protection scheme is to detect, localize and isolate faults fast and accurately, in order to minimize the effects of disturbances to the supply. The design of the protection scheme depends on a number of aspects, namely the type of faults, which can occur, their severity, the type of protection devices required, primary detection methods, backup protection, measures to prevent faults and measures to prevent incorrect operation of the protection system.

The key challenges associated with DC networks include: the lack of standardization, the unavailability of DC compatible products and protection devices, and topology dependence of protection, protection devices coordination and the relative lack of experience. New simple protection system design with a well defined setting calculation methodology is a crucial requirement for the practical implementation of DCMGs.

#### 1.2.1. Research Gap

Standards for DCMG protection and grounding are not available as of today. Devising a suitable grounding strategy, which could facilitate reliable fault detection, and limit touch voltages to safe limits is important in developing DCMGs as a common power system solution

Although there are certain DCMG fault detection techniques proposed in literature, protection of DCMGs using those techniques is not straightforward due to the following reasons:

- **High sensitivity of network response to fault impedance** short current rise time imposing strict time limitations for fault interruption.

- Most techniques rely on communication between devices- the requirement for multi-terminal measurements, accuracy is affected by sensor and communication errors, high cost of implementation due to additional sensory and communication requirements and requirement of synchronized measurements.

- The intermittent nature of DGs connected to the network, different loading levels and different modes of operation of microgrids- changing fault level and changing power flow direction pose challenges to relay coordination.

#### 1.2.2. Main Objectives

The main objective of the research is to design a protection and grounding scheme for DC microgrid systems.

The following specific objectives are to be used to address the above main objective:

# 1) To identify the DC microgrid grounding schemes, which could facilitate,

- Reliable fault detection,

- Limit ground fault currents and touch voltages to safe limits

- Ground fault override capability

- 2) To assess the fault characteristics of DC microgrids under different fault events by,

- analyzing the transient fault signals using signal processing techniques and,

- extracting characteristic features

- 3) To design an effective protection scheme to detect, localize and isolate faults within safe time limits.

- It is hypothesized that signatures in high frequency currents during transients contain information about the disturbances, and it can be used for reliable fault detection and localization.

- Design involves the use of extracted features with a pattern recognition technique to develop an intelligent and adaptive protection scheme.

## **1.3. Thesis Overview**

The rest of the report is organized as follows:

Chapter 2 presents the literature review covering the area of (i) DC microgrid fault detection and localization, (ii) protection coordination, and (iii) fault interruption equipment.

Chapter 3 presents the development of DC microgrid test system covering the control techniques employed in DC microgrid network. Battery management, current sharing between DGs and other control capabilities of the developed model are evaluated under this chapter.

An in-depth analysis of fault response of DC microgrid network is provided in chapter 4. Individual converter and overall system behavior are investigated here to gain insights into the DC microgrid protection requirements.

Ground fault response of the DCMG network under different grounding configurations is analysed in chapter 5. Design considerations for selecting a grounding arrangement are discussed in this chapter.

The proposed fault detection and localization algorithm is introduced in chapter 6. How the proposed scheme could be incorporated to maintain proper coordination between devices and achieve selective isolation capability also discussed under this chapter. The theoretical basis and methodology behind discrete wavelet transform (DWT) multi-resolution analysis for fault feature extraction is discussed. Step by step approach on how the feature vector is constructed for fault classification is presented under this chapter. Furthermore, the use of artificial neural networks (ANNs) for fault classification is discussed in detail. Different configurations for fault non fault simulations that are used to generate data for ANN training and testing are discussed in this chapter.

Chapter 7 presents the performance evaluation of the proposed fault detection and localization scheme giving a comparative analysis against the existing fault detection techniques.

Finally in chapter 8 conclusions and main contributions are presented identifying the areas of future research.

#### 2. LITERATURE REVIEW

With the new developments in the renewable energy field, DC distribution networks have drawn considerable research attention. More recently, many works of literature on protection schemes and fault interruption equipment have been published. This chapter discusses on various fault detection and localization schemes and fault interruption equipment proposed.

# 2.1. DC microgrid protection challenges

Developing a network protection scheme is a comprehensive task that involves several challenges [13,14]. Key requirements of DC Microgrid (DCMG) protection and challenges involved are reviewed in this Section. The main protection requirements include, (i) Personnel and equipment safety, (ii) Reliable fault detection capability, (iii) Timely fault detection capability, (iv) Reliable operation with minimum loss of power to the unfaulted sections, (v) Fault ride-through capability under temporary faults, and (vi) Ability to provide backup protection. These requirements must be weighed against the cost of devising a protection scheme [13-18].

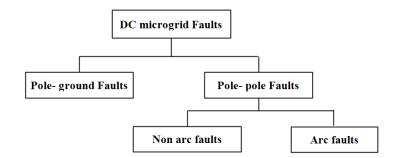

# 2.1.1. DC microgrids faults

Possible fault types of DCMG systems are pole-pole faults and pole–ground faults [15]. Among these, pole–ground faults are the most commonly seen type. Power electronic converters connected to the network may experience internal switch faults that can cause pole–pole faults, which requires the replacement of the device. Pole–pole faults are most often low resistance faults while pole–ground fault can be either low resistance faults or high resistance faults [14,15].

In addition, arc faults can occur at different locations of DCMG, and are difficult to detect due to very high arc fault resistance involved. Faults in DCMG systems can be classified as shown in Figure 2.1.

Figure 2. 1 Classification of DC microgrid Faults

# 2.1.2. Challenges: Fault detection and localization

AC power systems have several protection standards and guidelines, which can be easily adopted for AC microgrids (ACMGs). Contrarily, standards for the protection of DC microgrids are still under development [16]. In addition, unlike for DC systems protection equipment for AC systems are well developed and commonly available.

The absence of effective DC fault detection techniques presents a major barrier against the adoption of DCMGs. Overcurrent and differential elements are used typically for the protection of DC networks in a wide range of applications. However, due to the intermittent nature of DGs connected to the network and different operational modes of the DCMG protection using the conventional protection schemes is not straight forward; changing fault levels and power flow direction impose challenges in fault detection and relays coordination [14, 19]. In addition, it may result in poor fault discrimination and can result in loss of power to the healthy sections of the network. As a result, conventional DC fault protection techniques cannot meet the DCMG protection requirements, and there is a need for the development of fast and accurate DC fault detection scheme [14-20].

Fault localization is required for fast isolation of the faulted zone of the distribution network, and is an essential requirement for quick recovery of the system. Line impedance and traveling wave based techniques have been adopted as an industry standard for fault localization in AC distribution networks [21]. The absence of frequency and phasor information in DC systems prevents the line impedance based techniques to be employed directly [22, 23]. Furthermore, traveling wave based methods for fault localization cannot be employed due to the short lengths of distribution cables.

#### 2.1.3. Challenges: fault current interruption

In AC, the natural zero crossing facilitates the self-extinction of the arc between parting contacts of mechanical breakers. However, in DC, there is no zerocrossing and requires an additional mechanism to force the current to zero [14, 15, 24-26]. In practice, AC circuit breakers (ACCBs) are used for fault interruption in DC networks, with a significant voltage and current derating [27, 28]. In addition, specially constructed mechanical circuit breakers (CBs) with arc chutes are used to dissipate and cool the arc [25]. However, these setups are expensive and require a large space.

Power electronic converters have a limited overcurrent withstand capability, typically in the range 2-3 times nominal load current for few tens of microseconds. Initially, after a fault, DC link capacitors discharges instantly giving rise to fault current with very short rise time and high magnitude. Hence, faults in DCMGs should be detected and isolated, in a timely manner [14, 28]. Due to considerably long operation time of electromechanical CBs (typically longer than 10 ms), they cannot meet the required time limits for DC systems [23, 29]. DC circuit breakers and fault current limiting converters have drawn considerable attention recently as an effective solution for DC fault interruption [30]. However, they are state of the art devices, which incur high costs. Furthermore, considering the high on-state power losses, large volume and weight due to additional cooling requirement, and high susceptibility to transient over-voltages, it is open to question as to whether they offer an effective solution [14, 30, 31].

## 2.2. DC microgrid fault detection and localization schemes

Reliable fault detection and localization scheme is essential for the safe operation of DCMGs. Compared to the AC networks, DCMG protection techniques are still in its early stage of development. Furthermore, as discussed in Section 2.1, the absence of frequency and phasor information in DC systems prevents the direct adoption of distance protection techniques well-established for AC networks [20, 21].

Existing knowledge on the protection of DC networks in the areas of telecommunication and data center DC networks, MVDC shipboard and traction networks is useful when developing a DCMG protection technique. However,

compared to these networks, fault detection in DCMGs is more difficult due to their smaller scale, several interfacing DGs in DCMGs, multi-terminal nature of the network and high safety requirements. Hence, different protection methods are required for DCMG networks [20].

In designing fault detection scheme for a power distribution network, there are several factors to be considered: (i) fault type, (ii) severity of the fault, (iii) network configuration, (iv) network grounding configuration, (v) safe time limits for fault interruption, (vi) available fault interruption switchgear, (vii) requirement for backup protection and (viii) Preventing false operation of the relays. Furthermore, coordination between component level (eg :- IGBTs), device level (eg: - VSC) and system-level protection schemes should be maintained [13,14, 20, 32].

Different fault detection methods in DCMG networks and their effectiveness are reviewed under the criteria: accuracy of fault detection, ability to localize faults, requirement of additional communication and sensory equipment, cost and ease of implementation.

# 2.2.1. Overcurrent detection

Overcurrent schemes are generally employed in both AC and DC networks. However, conventional overcurrent schemes for the protection of DCMGs give rise to several protection issues.

The magnitude of fault current in a DCMG depends on network architecture, operating mode of the network (islanded or grid-connected), converters employed to interface DGs, fault parameters and type of fault. Varying fault current magnitude and direction of power flow can cause false operation of overcurrent relays and delayed /non-operation [14, 19, 20]. In [33] a smart relay utilizing the current and voltage magnitude for DCMG fault detection is presented. In this scheme, the relays are built-in with the power electronic converters, and the relays operate autonomously if a fault is detected. If the converter current surpass a preset value and stays above beyond a preset time limit, and at the same time voltage drops below 0.8 pu, a fault is detected by the proposed relaying scheme. In [34], a two-section overcurrent detection technique is proposed for MVDC lines. In this scheme an instantaneous overcurrent threshold is used for primary protection and overcurrent threshold with a time delay for the backup protection scheme. The inability to detect

high impedance faults, and inability to locate the faults, and the absence of selectivity in fault isolation are the major drawbacks of these schemes proposed in the literature.

The use of Intelligent Electronic Devices (IEDs) for fault detection is proposed in [22]. DC Current measurements at IED locations are measured using IEDs are utilized for overcurrent and differential protection. These techniques allow selective isolation of faulty section without interrupting the supply to the healthy parts of the network. Furthermore, differential protection enables high impedance fault detection capability. In [35], a similar technique using IEDs is presented, where current magnitudes, direction and bus voltage levels are monitored by IEDs at different locations for fault detection.

# 2.2.2. Derivatives of current

Use of rate of change of current (di/dt) for quick detection of DC faults is investigated in [20]. The fast discharge of the DC converter capacitors results in high magnitude fault current with a short time constant. This transient current is damped by fault current loop impedance. To prevent the total discharge of network capacitors following a fault, a fast fault detection method is required. Hence, di/dt based protection schemes are deemed suitable for DC networks compared to other schemes due to its fast fault detection capability [20, 36].

In [37], fault detection technique utilizing the initial di/dt value is presented. This fault detection technique based on initial value of di/dt utilizes initial response of DC network capacitance to a fault for detection of faults, and to estimate the location of the fault. Similar initial response for both low and high impedance fault was observed in this study, hence allows the identification of faults unaffected by fault impedance. However, under high impedance faults, di/dt decays fast compared to during low impedance faults. Analyzing the initial di/dt response allows the detection of high impedance fault situations [37]. Although di/dt schemes facilitate very fast fault detection, the detection accuracy of this technique is gravely affected by measurement noise and disturbances in the network [19, 20, 37].

#### 2.2.3. Differential protection

Differential protection can be used to protect predefined zones of protection in the network. The existence of DGs, varying load conditions resulting in different fault current levels and changing power flow direction has no impact on differential schemes; hence, offer a reliable protection solution for both AC and DC networks [14, 19, 22].

In [38], differential protection scheme with master controller and two slave controllers for each protection zone is proposed. The currents at the both ends of the protection zone are measured by the slave controllers, and are communicated to the master controller. In the event of a fault, the difference of current magnitudes at either ends of the protected element differs allowing the fault to be detected by the master controller.

Differential techniques depend on communication of devices monitoring line current at the two ends of protective zone. Hence, considering the communication time delay between devices, and maintaining proper synchronization among devices is important when designing a differential protection scheme for the network.

#### 2.2.4. Distance protection

AC networks employ distance protection schemes for the localization of faults in the network. However, frequency information are inherently absent in DC systems, which prevents the direct adoption of these distance protection schemes in DC networks. Furthermore, during a fault transient in a DC network, voltage and current waveforms oscillate rapidly and frequency varies; hence, it is difficult to define a fundamental frequency [14]. In [39, 40] novel technique for the network parameter calculation in order to determine the DC network impedance under a defined frequency is proposed. This allows the detection of faults, and distance to the faults using the distance protection principles.

In [39], the impedance estimation scheme, which does not require an external signal injection source, is proposed. A distance protection scheme using active impedance measurement for DC shipboard networks is proposed in [40]. In this proposed scheme, a wide frequency current signal is injected and the resulting voltage is measured to determine the equivalent network impedance to be used with the distance protection scheme.

# 2.2.5. Signal processing based detection schemes

Fast Fourier transforms (FFT) is less useful in analyzing a dynamic signal due to the absence of time scale information. Hence, the use of FFT for power system signal processing applications is limited [41]. Short-time Fourier transform (STFT) analyses signals in both time and frequency domains, and is a widely employed tool for power system signal processing [41, 42]. The use of STFT for quantitative analyses of high frequencies during a fault transient in DC network is discussed in [43]. However, achievable time and frequency resolution using the STFT is limited due to constraints on the selection window size. Narrow time window will give good time resolution at the expense of frequency resolution. On the other hand, a wide time window will result in good frequency resolution but poor time resolution [14].

Wavelet transform (WT) analyses a signal in both time and frequency domains under multiple resolutions. Hence, compared to STFT and FFT techniques, WT is capable of giving better time and frequency resolution of the signal; hence is popularly used for signal processing applications. Wavelet representation of a signal provides a good representation of the time variation of the frequency contained within the signal. Wavelet multi-resolution analysis techniques have been used for wide range power system applications, including network fault detection and recognition of transient events [44-57].

The common methodology for the use of wavelet transformation for fault detection is to extract the unique features of fault signal using wavelet decomposition, and to use these quantified features as variables with an algorithm to determine fault situations [14]. Literature discuss different techniques to capture these characteristic features. One technique is to compute and compare the magnitude of detail coefficients to identify characteristic changes in the signals [45]. However, employing raw wavelet coefficients values for fault detection requires large memory space and computing time. In [41], wavelet decomposition based fault detection technique for medium voltage (MV) shipboard networks is presented. This method uses the energy variations in different decomposition levels to identify characteristic changes in the signal during the fault in the network. This reduces the required memory space and processing requirements for fault detection. In addition, the use of several statistical parameters for fault feature identification from the wavelet decomposed signal is discussed in the literature [45, 47].

#### 2.2.6. Pattern recognition schemes

Recently, data-driven pattern recognition techniques have garnered continuous interest, especially for power system applications. Not having to define hard thresholds is a major strength of fault detection techniques based on pattern recognition. It helps in intelligent and accurate fault detection unaffected by changes in the network conditions.

Artificial neural networks (ANNs) have been tested for fault classification in AC, HVDC and MVDC networks, and have demonstrated that they are fast, accurate and robust in its performance [47-53]. The ANNs are required to be trained using fault data obtained under different network operating conditions, fault types and fault locations to ensure correct fault detection unaffected by fault parameters and changes in the network. These pattern recognition based techniques have shown a vast potential in several fields of engineering applications and shows promising results in several power system protection applications.

## 2.3. DC microgrid protection coordination schemes

Coordination among protection devices is essential for minimizing fault clearing time, facilitating fast restoration of power and to minimizing power outages in the network. Differential fault detection techniques with bounded zones of protection are proposed in [22, 38]. However, these schemes are incapable of providing backup protection to the adjoining protection zones. This is a major drawback associated with these protection coordination schemes.

Primary protection relays operates as the main protection relay for a component or bounded zone of the network. Backup protection relays are required to operate in the events of primary protection relay or breaker failures. The protection coordination method is selected based on protection methods deployed, fault clearing time limits, ability to distinguish between temporary and permanent faults, and ability to ride-through fault events [14].

The commonly used protection coordination methods employed in DCMGs is through relay time grading and communication between relays, and is discussed in the sections below.

#### 2.3.1. Protection coordination: time grading of relays

In time graded relays, relay operating times are set in a way primary protection relays protecting the faulted section operates first. Relay time grading requires the backup relays to operate, if the primary protection fails [14].

The coordination method between fast-acting fuses and circuit breakers for coordinated protection of DCMG is proposed in [54]. Fast-acting fuses placed at selected locations of the network is capable of fast fault clearance, and compared to circuit breakers is cost effective. Time graded overcurrent relays built into circuit breakers are positioned to isolate zones/components of the network in case of a fault.

Protection coordination scheme among fuses, relays and converters with fault current limiting capability is presented in [33]. Fast-acting fuses are employed as the main protection device within the AC zones of the network. Fast-acting relays, which act faster than the fuses are used to clear faults in the DC side, thereby avoiding the blow off of fuses for DC side faults in the network.

# 2.3.2. Protection coordination: communication based

Coordination between relays based on communication among relays is a reliable solution for DCMG systems. In [22] Intelligent Electronic Devices (IEDs) are positioned at selected locations of the network, and inter device communication method is used to keep the coordination between these devices. A similar relay coordination approach is presented in [10], where voltage and current waveforms monitored at relay locations are communicated between relays to determine occurrences of faults and fault locations. A reliable communication channel is important for protection coordination; hence, is affected by failures in the communication channel, and communication delays should be accounted for.

#### 2.4. DC microgrid fault interruption

To ensure safe operation of distribution networks, appropriate fault interruption equipment are required, either to interrupt fault currents or to isolate faulty sections in the network. As discussed previously, DC networks impose stringent requirements for interrupting fault current. Fast fault current rise requires the fault to be interrupted within a very short time span. Furthermore, the absence of natural zero crossing in the DC current requires fault interruption switchgear to force the current to zero using an alternate method. Hence, DC compatible interruption devices are required, which can operate very fast, and with a special assembly for DC current breaking [14, 20, 22, 23].

In [20, 23], fault current interruption time limits for a voltage source converter (VSC) based DC networks are assessed. Preventing transient over-voltages during fault interruption, fault detection time, power losses within the breakers, implementation cost, coordination between protection devices and continuity of supply to the healthy sections are important factors to be considered in the selection of switchgear for DCMG network.

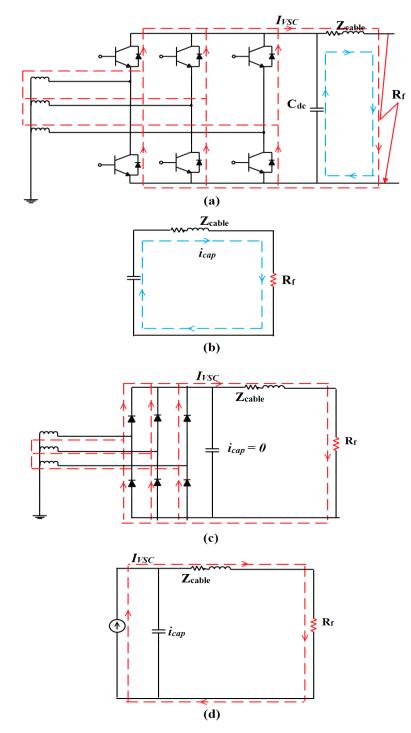

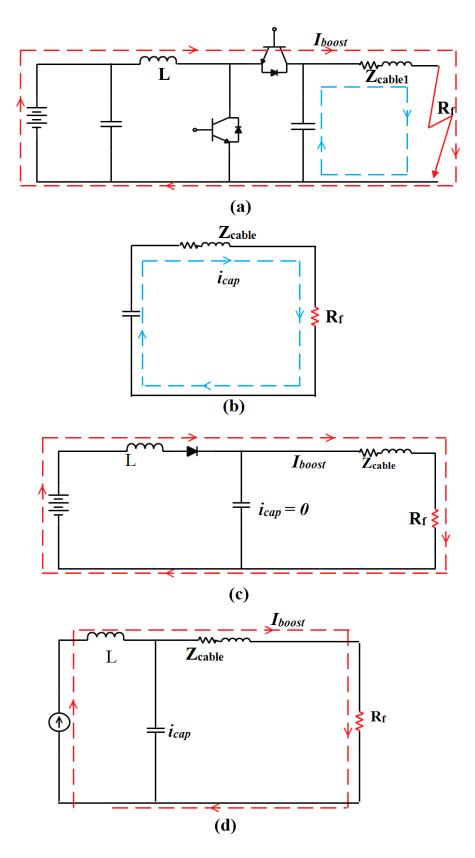

# 2.4.1. Converter fault current blocking and current limiting techniques.

Power electronic converter architectures with fault current blocking capability are commonly employed in HVDC networks and MVDC shipboard and traction networks. They are capable of quickly blocking the currents through converter controls. In practice, IGBT converters are embedded with IGBT self-protection schemes (both overvoltage and overcurrent), which activates under fault conditions [55, 56]. However, with IGBTs blocked, in conventional converter architectures, such as two level VSCs and DC-DC buck/boost converters, the fault currents will start to flow through freewheeling diodes. These diode freewheeling currents will only be limited by cable and fault impedances. It is not possible to achieve converter blocking with conventional VSC and DC-DC converters, and specially constructed converters with current blocking ability are required [14, 20, 57].

Under normal operation, power electronic converters are capable of limiting maximum current flow. However, most of the conventional converter models cannot limit fault current due to the existence of freewheeling diodes. In [57-64], specially designed converter model with current limiting ability when a fault in the network is detected is presented. These fault current limiting converter architectures employ multi-mode control schemes, which change the control parameters to limit current flow through the converter when a fault is detected. Current limiting converters work in coordination with other protection devices to minimize the damages to the network by fault current, and to prevent loss of power for prolonged periods during temporary faults. Loss of supply to the whole network including the healthy sections of the network is a major drawback of this method [14]. Fault current blocking converter architectures proposed for DC networks are presented below.

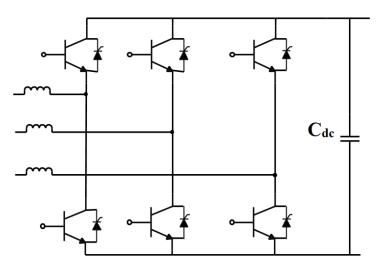

#### 1. ETO thyristor converter architectures

Replacing the freewheeling diodes of conventional IGBT based VSC architecture by ETO thyristors is proposed in [33], to enable current blocking capability. In these converters, converter does not provide a diode freewheeling path for the fault current to flow, as in IGBT converters. The converter architecture is shown in Figure 2.2. The ETOs have a high current and voltage handling capability. In addition, they have lenient switching requirements compared with IGBTs. Once a fault is detected, soft shut-down method is employed, where the ETO gate voltage is gradually reduced to prevent transient over-voltages during current blocking [33, 57, 58].

Figure 2. 2. ETO thyristor based VSC architecture.

2. Back-to-back VSC converter architecture

Back-to-back VSCs (see Figure 2.3) feature voltage and current regulation capability on both sides of the converter. In addition, this converter is also capable of blocking fault currents during a fault on either side [59, 60].

Back-to-back converter architecture uses two active VSCs; hence, increases the cost and converter size. The presence of two conversion stages also increases the power losses associated with the converter.

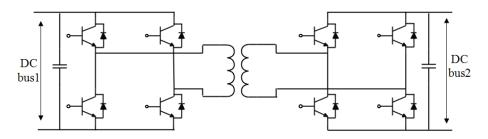

Figure 2. 3 Back to back VSC architecture

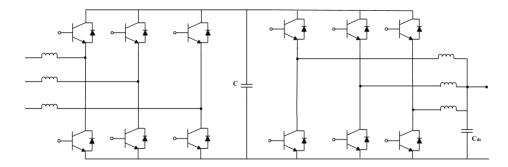

# 3. Isolated DC-DC converter

DC-DC converter architectures based on isolation transformer, which is capable of controlling/blocking current during faults are proposed in [59, 62-64]. Dual active bridge (DAB) converter architecture based on two full-bridge converters through a high frequency transformer is shown in Figure 2.4. In addition, DAB based isolated DC-DC converters are capable of limiting fault current on both sides of the DAB [15, 59].

The literature discusses several modular multilevel DAB architectures for both high and medium power applications [59, 61, 65]. However since they require a high number of power electronic switches and have several conversion stages, modular multilevel converters are conventionally used in HVDC networks and are less cost-effective with LVDC and MVDC networks [14]. Recently developed wideband gap (WBG) devices (eg:- silicon carbide (SiC) and Gallium nitride (GaN)) with their low on-state losses and other favorable traits presents a possibility to fully utilize the abilities of these converter architectures for LVDC and MVDC applications [15,66,67-69].

Figure 2. 4 DAB architecture with DC fault current limiting capability

#### 2.4.2. Fault current limiters (FCLs)

Fault current limiters (FCLs) can be utilized in DC networks to limit fault currents when a fault is detected [70]., FCLs have a zero impedance under normal operation, and. internal impedance increases once a fault is detected, in an effort to limit fault current flowing through the FCL. The strategic placement of FCLs for the protection of distribution networks is studied in [70, 71]. These studies show that the point of connection of DGs to the power network is the optimum position to connect the FCL for fault current limitation.

The connection of protective inductors at power electronic converter terminals to limit current transients within HVDC networks is studied in [72]. However, the requirement of a large iron core, which as a result increase the size, weight and cost of installation, is the main drawback of this technique. Furthermore, this FCL arrangement is only capable of limiting time varying currents and is not effective during steady fault currents.

The FCL technology based on superconductor materials is discussed in [74-75]. These FCLs operate as a superconductor under normal operating conditions and when the current reaches a critical level, it changes the superconducting state to increase the resistance, thereby effectively limiting the current. Design criteria and selection of parameters for superconductor based FCLs considering the power network requirements are presented in [73]. One of the main disadvantages of FCLs is the requirement of long lengths of superconducting materials; hence FCLs are large, heavy and expensive.

Solid-state FCL designs for DC networks are presented in [76, 77]. Smaller size, fast response times and enhanced control capabilities are major advantages associated with solid-state FCLs. However, solid-state FCLs have a high conduction loss, which is a main drawback.

# 2.4.3. Fault current interruption with DC side circuit breakers

DC fault current interruption techniques using DC CBs have been discussed in [23,28,78,79]. These techniques offer selective fault interruption capability, allowing zones of the network unaffected by the fault to continue operation.

As discussed in Section 2.1, due to the absence of a zero-crossing in the DC current waveform, breakers face a unique challenge of no natural method for extinguishing the arc that occurs during current breaking.

The use of reactors in series with the conventional ACCBs to interrupt DC fault current is discussed in [78]. Due to the mechanical constrictions, ACCBs cannot meet the time limits for fault current interruption in DC networks. Regardless of the fact that AC breakers being a mature technology offer advantages such as low cost, DCCBs are a better solution for DC networks as they can achieve timely DC fault isolation. Several DC breaker designs; mechanical, solid-state and hybrid (solid-state and mechanical) have been proposed and developed recently for DC applications ranging from LVDC, MVDC and HVDC.

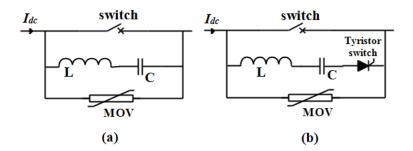

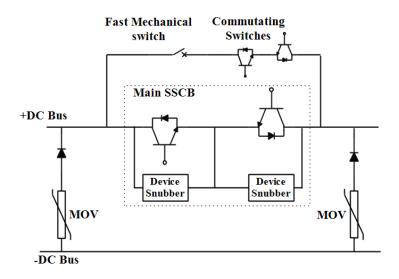

## 1. Mechanical DC breakers

Mechanical DC breakers are based on the principle of resonance, where oscillation circuits are employed to create a zero-crossing point artificially. In Figure 2.5 mechanical DCCBs circuit with passive (Figure 2.5(a) and active (Figure 2.5(b) commutation circuitry are shown [24, 80, 81]. Mechanical DCCBs comprises of a mechanical switch and resonance circuit for force commutation. In addition, metal oxide varistors (MOVs) are used to absorb energy during the current interruption. When a fault is detected the mechanical switch is opened and the current is commutated through the commutation circuitry. The resonance circuit (capacitor and inductor arranged in series) creates an oscillating current, and creates a zero-crossing point between contacts of the mechanical switch. Then mechanical switch can open at zero current [15]. Mechanical DC breaker response time is much slower (~30 ms) than DC link capacitor discharge due to mechanical constrictions. Hence, the network has to undergo high fault current transient, during a fault before the fault is interrupted.

Figure 2. 5 Mechanical DC breakers with (a) passive commutation, (b) active commutation circuit.

2. Solid-state circuit breakers

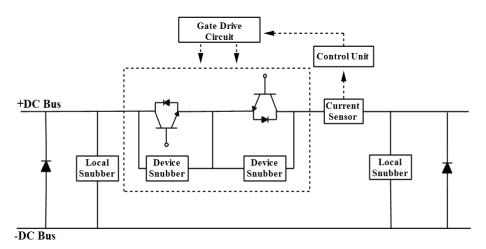

Solid-state circuit breakers (SSCBs) offers a promising solution for DCMG fault interruption with its fast current breaking and high constant current handling capability compared to other devices. The literature discusses several SSCB designs based on, ETOs, GTOs, IGBTs and IGCTs for DC current breaking [14, 15, 28].

Modified SSCB assembly with bidirectional power flow capability is shown in Figure 2.6. The proposed breaker design uses a string of series connected solid-state switches in order to handle the transient voltages safely during the current interruption, and prevents the transients exceeding the withstand levels of the power electronic switches. IGBTs are often the common choice in these breaker designs because of wide commercial availability and fast response capability. However, for high power applications, IGCTs are preferred over IGBTs due to their low conduction losses and rugged structure [28].

Figure 2. 6 Solid-state circuit breaker assembly.

Figure 2.6 shows the SSCB design, which provides the functionality of the complete CB assembly. Fault detection is carried out by the breaker controls scheme itself; hence, external fault detection relays are not required. When a fault, occurs

the control unit signal the gate drive circuit and turns off IGBT switches. Snubber circuit and freewheeling diodes dissipate the energy during the current breaking [24,28,82].

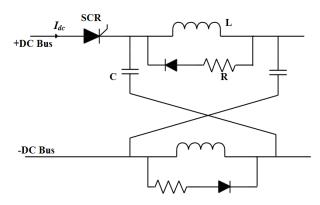

In this SSCB design, solid-state switches must be actively driven OFF before current level exceeds the interrupt capability of the power electronic switch. Hence, fast fault detection within the time limits is a necessity. To overcome these limitations, Z source circuit breaker (ZSCB) design (see Figure 2.7) is proposed in [24]. Unlike the SSCB, ZSCB absorbs part of the large transient fault current to create a current zero-crossing. Silicon control rectifier (SCR) is naturally turned off once the zero-crossing is created. Natural commutation of the solid-state switches facilitates the fault to be isolated, without having to force commutate. In addition, passive elements used in ZSCBs limits the peak current within the solid-state devices. Hence, these are not required to withstand high currents.

The ZSCB design proposed in [24] has some drawbacks, such as the inability to protect against overload conditions and only being able to interrupt faults with high fault transients. In addition, for less severe faults, fault current transient energy may not suffice for natural commutation. ZSCB design which, adopts a separate force commutation circuitry is proposed in [83]. In addition, ZSCB circuitry has been modified to achieve bidirectional power flow capability in [60].

Figure 2. 7 Z source circuit breaker circuitry

Although SSCBs devices offer a feasible solution of DC fault interruption, they mostly rely on additional sensing, processing and control. Furthermore, they employ additional cooling systems, and incur considerable power losses at solid-state device junctions. The capability to use SiC and GaN wideband gap devices to address the issue of losses at semiconductor junctions has been investigated [15,24,83,84]. It is presumed the performance of SSCB technologies to be improved by using WBG device technology.

#### 3. Hybrid CBs (HCBs)

Hybrid CBs (HCBs) is an alternative to address the issue of high conduction losses of SSCBs, HCB is a combination of SSCB and bypass branch, which consists of commutating switches in series with fast mechanical switch (FMS) as shown in Figure 2.8. Under normal operation, current flows through the bypass branch of the HCB [85-90]. When fault current is detected, the commutating switch is turned OFF to pass the current through the branch of SSCBs. This allows the FMS to be opened at zero current. Then the current through the SSCB branch is blocked by the SCCB assembly. Possible transient interrupt voltage during fault interruption is handled by MOVs. The MOVs also absorb inductive energy in the line following the current interruption. Practical realizations of HCBs are discussed in [86-89].

In this setup low voltage commutating switches are adequate to commutate current to SSCB branch; hence, low conduction losses are incurred. Due to the very short ON state, solid-state devices do not require additional cooling, allowing HCBs to be built at low cost and compact compared to SSCBs. Although HCBs provide advantages of both mechanical and solid-state breaker technologies, due to mechanical constrictions, HCBs have relatively slow operating speed compared to SSCBs (typically between 500 µs-2 ms) [14, 31, 90].

Figure 2. 8 Hybrid circuit breaker circuitry

# 2.5. DC microgrid modeling, control, experimental setups and standardizations aspects

An increasing number of research work on DCMG have been carried out, covering application in the area of smart DC homes/ buildings, EV charging stations, transit networks, and telecommunication networks. When designing a DCMG key issues to be considered are; (i) swift current sharing between RESs, (ii) achieving economic and autonomous operation, and (ii) catering the intermittent nature of RESs to maintain reliable power supply.

# 2.5.1. Overview on DC microgrid architectures

Driven by the practical requirements, several DCMG topologies have been proposed. The criteria considered are, system reliability, robustness and control flexibility. As these criteria are often conflicting with each other, different compromises are taken into account when deciding the most suitable microgrid configuration for a particular application [4, 91-93].

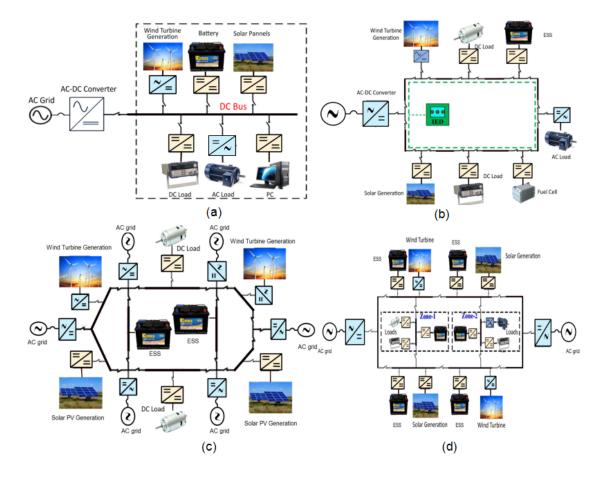

# 1. DC microgrid network topologies

A number of DCMG network topologies are reported in the literature and some of the most common configurations are assessed in this Section.

For the purpose of our study, the topologies of DCMGs are classified into four categories: (i) Radial configuration, (ii) Ring configuration, (iii) Mesh configuration and (iv) Zonal type configuration and are shown in Figure 2. 9 [5, 94, 95]. While radial network topology has simpler control requirements, more complex network architectures such as ring, mesh and zonal topology provide better operational reliability and flexible control capabilities. However, main drawback when of complex network topologies are: high cost of implementations, complex power flow management and relay coordination issues.

Figure 2. 9 DC microgrid with (i) Radial configuration, (ii) Ring configuration, (iii) Mesh configuration and (iv) Zonal type configuration

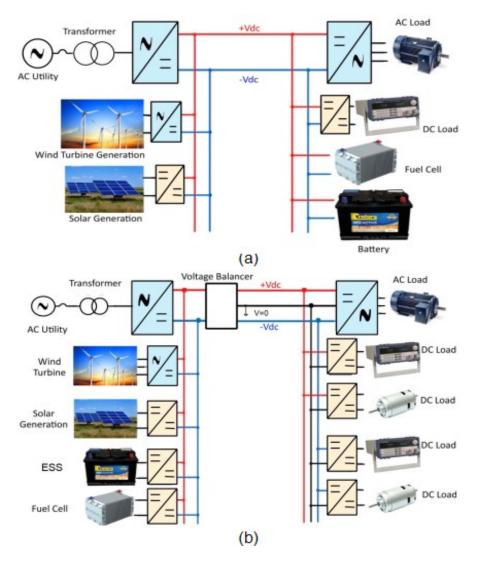

## 2. DC microgrid voltage polarity

The power in the DCMG system can be transmitted using two-wire (unipolar) or three-wire (bipolar) system. The difference between unipolar and bipolar DC systems is the number of selectable voltage levels [94, 96, 97].

## A. Unipolar DC microgrid system:

In the Unipolar DC system, sources, converters and loads are connected between two wires. The positive and negative pole of the DC bus as shown in Figure 2.10 (a). Since energy is transmitted over the DC bus at one voltage level, the selection of that voltage level is based on the requirement of the end-user. Proper selection of voltage level can decrease the number of DC-DC converters connected to the network. The main concern in the selection of the voltage level is that, with low voltage level, the transmission distance is limited while the high voltage level increases the safety risks [94, 97].

Figure 2. 10 DC microgrid with (a) unipolar DC bus, (b) bipolar DC bus

# B. Bipolar DC microgrid system

The bipolar DC system can overcome the above mentioned limitations of the unipolar system. The bipolar DC system consists of  $+V_{dc}$ ,  $-V_{dc}$  and neutral line as in Figure 2.10 (b). Consumers have the option to choose between three voltage levels  $+V_{dc}$ ,  $-V_{dc}$  and  $2V_{dc}$ . This decreases the number of DC-DC converters required to connect loads to the microgrid. A bipolar system offers more flexibility towards different loads. For example, ESSs can be connected to a one pole together with loads requiring high reliability. Furthermore, all renewable energy sources (RESs) can be connected to one pole with loads that should only be run when there is enough power [94, 95, 97].

## 3. AC grid interface of DC microgrids

The interface between DCMG and AC utility grid is important as it determines how electrical power flows between AC and DC networks. In modern DCMGs, AC grid interface is designed to facilitate bidirectional power flow allowing the excess energy generated by RESs to be transferred back to the AC grid. There are several AC-DC converter topologies discussed in literature covering both unidirectional and bidirectional power converter topologies. In some DCMG architectures multiple parallel AC-DC converters are used to increase the reliability and flexibility of the supply. These different interfacing AC-DC converter topologies have a significant impact on the selection of the DCMG architecture, control strategy, grounding and protection schemes.

Two-level Voltage Source Converter (VSC) with Active Front End (AFE) filter is a commonly used AC-DC converter topology in DC distribution systems [94, 98, 99].

## 2.5.2. DC microgrid Control requirements

Renewable energy sources (RESs) connected to a microgrid system, such as solar PV and wind follow the meteorological conditions, while loads operate according to their own profile. This intermittent behavior urges controllable sources such as Energy storage system (ESS) and AC grid interface converters to accommodate the variable demands and balance the power.

Unlike AC microgrids, the control of DCMGs is much simpler in the sense that they do not require reactive power control, and only the voltage control is required. The system voltage is dependent on active power flow. In order to ensure the stability of the system, the active power flow within the DCMG must be balanced at all times ensuring DC voltage be maintained at the required level [100].

The main control objectives of a DCMG include

- 1) Regulating bus voltage and maintaining stability.

- 2) Efficient power sharing between interlinking converters, DGs, loads, other microgrids and external grid networks.

- 3) ESS management.

- Energy management during the grid-connected and islanded mode of operation.

- 5) Response to faults in the network.

DC microgrid stability refers to the ability of the system to maintain steady bus voltage and current sharing among DGs and loads after being subjected to a disturbance [101]. The stability of the DCMGs can be an important issue under high penetration of load converters, which behaves as constant power loads [102,103].

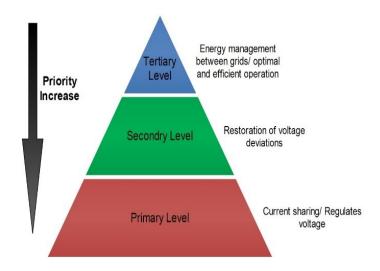

## 2.5.3. DC microgrid control hierarchy

The control of microgrids interfacing DGs has been extensively studied in the last few years. Several microgrid control architectures have been proposed in the literature [104-109].

Decentralized or centralized control using droop schemes are conventionally adopted in microgrids. However, with conventional droop control, there are inherent drawbacks of current sharing and voltage deviations. In addition, the microgrid is incapable of achieving a globally optimal control performance. To cope with these drawbacks, hierarchical control schemes were adopted [109,110]. With the increase of DGs connected to the network and complexity of the network, to achieve multiple control objectives, hierarchical control and energy management schemes have become essential.

The control of DGs in a DCMG can be achieved using different control architectures. Several such DCMG control architectures have been discussed in the literature. Five different control architectures, which can be categorized as: (a) Centralized control [104,105], (b) distributed autonomous control [106], (c) master-slave control [107], (d) multi-agent based control [109], and (e) hierarchical control, are discussed in literature. Among these decentralized control has advantages over other methods due to less reliance on communication, more autonomous and flexible control structure. Conversely, other control architectures are capable of providing better voltage control and current sharing among network DGs, compared to decentralized architecture. The choice of DCMG control architecture can vary according to the application (residential or commercial), or other features, such as size, topology, and location.

# 1. Centralized control

All available measurements of the considered microgrid are gathered in a central controller that determines the control actions for all units. The main advantage of centralized control is the central controller receives all available information, allowing it to achieve a globally optimal control performance. However, this method inherits several disadvantages including, heavy computational burden to the central controller, reliance on communication and not being scalable.

## 2. Decentralized control

Control architecture without any form of communication between local controllers. Mostly implemented as a droop control scheme (see Section 2.5.4), which uses droop characteristics that adjust active power output with locally measured DC voltage. This control architecture is capable of operating when all communication channels fail. However, optimal operation of the DCMG is rather difficult due to the lack of information to local controllers.

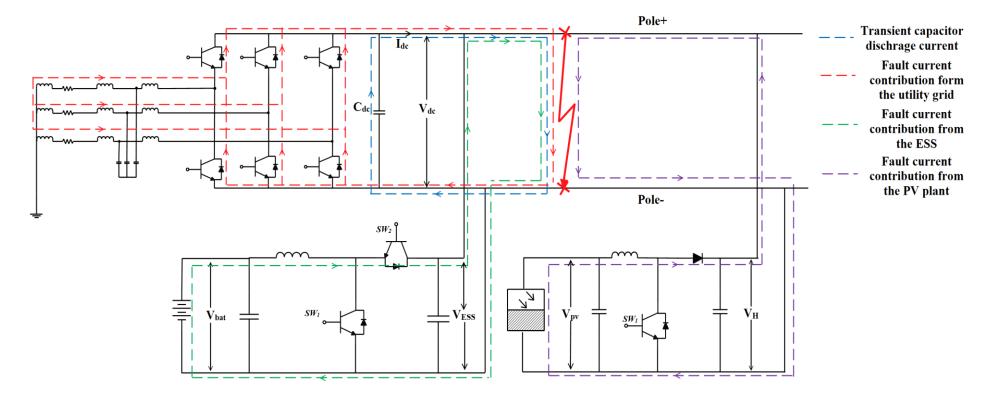

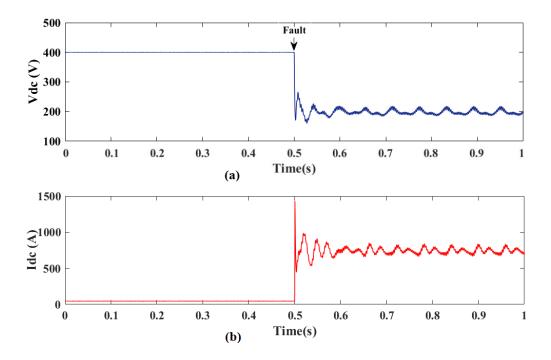

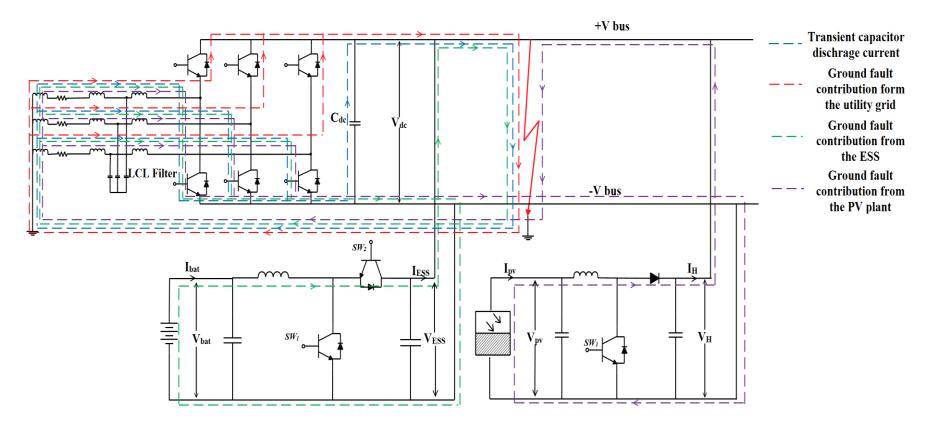

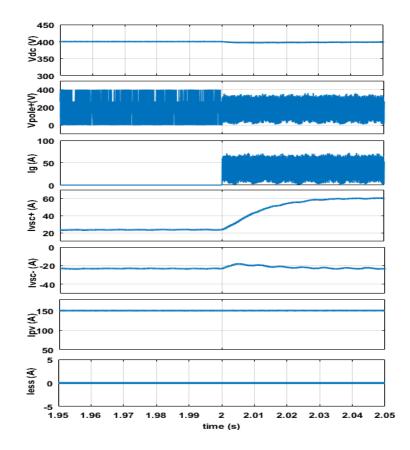

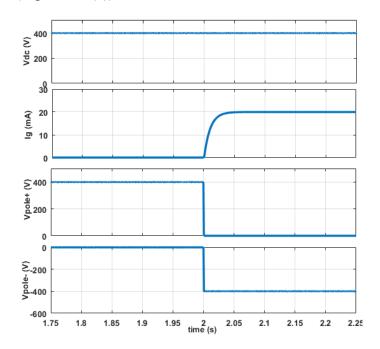

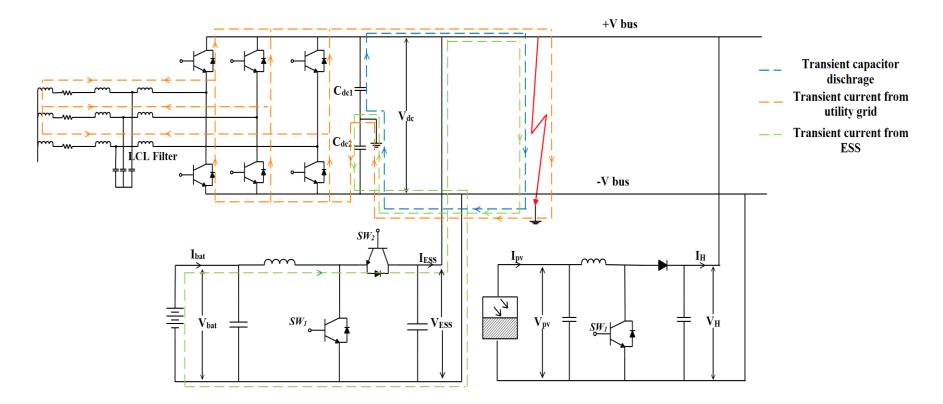

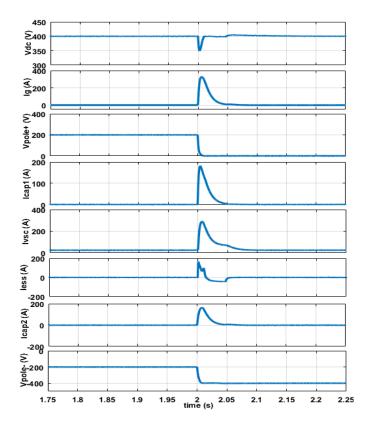

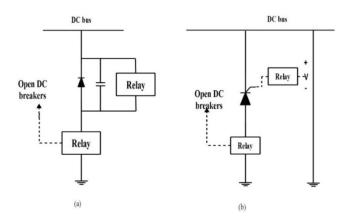

## 3. Master-slave control